National Instruments annonce un module pour le traitement par FPGA d’images transmises en Camera Link

04/09/2010

Le nouveau module NI 1483 ajoute la connectivité Camera Link à la plate-forme NI FlexRIO

National Instruments annonce la sortie d’une nouvelle solution de vision pour la plate-forme PXI intégrant une architecture de traitement parallèle hautes performances pour le cadencement matériel, le contrôle et le pré-traitement d’images.

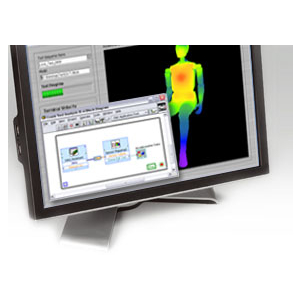

Cette solution combine le nouvel adaptateur NI 1483 pour l’acquisition d’images par Camera Link avec la carte FPGA (field-programmable gate array) NI FlexRIO, pour offrir des algorithmes de vision et de contrôle embarqués directement sur FPGA. Les FPGA peuvent être utilisés pour traiter et analyser une image en temps réel avec peu voire aucune intervention du microprocesseur. De plus, avec les FPGA, la conception de matériels personnalisés n’est plus indispensable.

Le nouveau module supporte des matériels Camera Link avec configurations de base, intermédiaire et complète ainsi que des configurations 10 zones, 80 bits, le tout jusqu’à 85 MHz. Cette conception permet aux ingénieurs et scientifiques de personnaliser l’acquisition d’images lorsqu’ils utilisent des capteurs personnalisés. La mesure à 85 MHz supporte la spécification normalisée Camera Link dans sa totalité, ce qui est particulièrement adapté aux applications avec des fréquences de trames élevées. Le module intègre également plusieurs options d’E/S, y compris quatre lignes d’E/S TTL, deux entrées opto-isolées et une entrée d’encodeur en quadrature en plus des nombreuses E/S modulaires et des options de communication industrielles disponibles pour la plate-forme PXI.

Les ingénieurs et scientifiques peuvent personnaliser le matériel NI FlexRIO à l’aide du Module LabVIEW FPGA sans connaissance des langages bas niveau de description de matériel ou de conception de cartes électroniques. En utilisant l’environnement de programmation graphique LabVIEW, ces derniers peuvent réduire considérablement leur temps de développement avec la possibilité de recourir à des IP VHDL existantes.